MEMORIAS.

a. Cuál es la función

principal de una memoria y cómo es físicamente.

b.

Cuáles son las diferencias entre las memorias RAM Y ROM.

c.

Qué es el CMOS, ROM-BIOS.

d.

Cuáles son las funciones

del BIOS.

e.

Cuáles son las características de las memorias dinámicas y estáticas

f.

Cuál es la función

principal de la memoria caché y cuantos tipos de caché hay.

g.

Explicar las

características de las memorias RAM dinámicas SIMM, DIMM, RIMM y DDR.

h.

Cuáles son los tipos,

velocidades y capacidades que manejan

las memorias DIMM.

i.

Cuáles son los tipos,

velocidades y capacidades que manejan

las memorias DDR.

j.

En qué consiste la

latencia y cómo interviene en el rendimiento de un computador.

A: Cuál es la función principal de una memoria y cómo es físicamente.

efinición / Uso / Función

Una memoria de computadora es un conjunto de pequeñas celdas numeradas. Más aún: cada una de esas celdas puede almacenar sólo entidades binarias (dígitos o símbolos que toman uno de dos valores discretos 0 o 1). Así, utilizando apropiadamente esas celdas es posible guardar fácil -pero exclusivamente- la información X en la celda Y. Sin embargo, la celda Y no puede almacenar otra información en el mismo instante de tiempo.

Dicho de otra forma, la memoria de una computadora es completamente localizada. Por supuesto, el número de celdas es muy grande. Una memoria de computadora es muy sistemática, muy ordenada, de ahí su eficiencia; pero al mismo tiempo es muy rígida. Eso significa que para tener acceso a una información se requiere saber exactamente en qué lugar preciso está almacenada. Así, es necesario dar a la máquina instrucciones del tipo: ``Leer la información que se encuentra almacenada en la celda 32767 y copiarla a la celda 26567''.

El uso de la memoria es para agilizar el flujo de información hacia el CPU. En otras palabras es como decir desde el disco duro al CPU hay mucha mas distancia y mucho mas tiempo es perdido mientras busca en el disco duro y manda al CPU para ser procesado, mientras que si la información que esta en el disco es cargada a la memoria de allí el CPU puede accesar mas rápidamente la información que ha sido pedida. También se puede decir que el uso de la memoria es agilizar la compilación de información.

La memoria tiene como función primordial almacenar temporalmente(en el caso del RAM) información del disco para ser ejecutada por el CPU, de una manera más ágil y veloz.

Tipos de Memoria

- Memorias con paridad consiste en añadir a cualquier de los tipos anteriores un chip que realiza una operación con los datos cuando entran en el chip y otra cuando salen. Si el resultado ha variado, se ha producido un error y los datos ya no son fiables. Dicho así, parece una ventaja; sin embargo, el ordenador solo avisa de que el error se ha producido, no lo corrige. Es mas, estos errores son tan improbables que la mayor parte de los chips no los sufren jamas aunque estén funcionando durante años; por ello, hacen que todas las memorias se fabrican sin paridad.

- Primaria:

- RAM: abreviatura para random access memory, en español vendría siendo memoria de acceso randomico. Este tipo de memoria se considera volátil ya que cada vez que la computadora es apagada esta memoria es totalmente eliminada y puesta en 0. Hay muchos tipos de RAM, como por ejemplo:

- DRAM: Dinamic - RAM, o RAM a secas, ya que es “la original”, y por tanto la más lenta. Este tipo de memoria fue usada desde la época del 386, su velocidad de refresco típica es de 80 ó 70 nanosegundos, tiempo este que tarda en vaciarse para poder dar entrada a la siguiente seria de datos. Por ello, es más rápida la de 70ns que la de 80ns. Físicamente, aparece en forma de DIMMs o de SIMMs, siendo estos últimos de 30 contactos.

- Fast Page(FPM): aveces llamado DRAM, puesto que evoluciona directamente de ella, y se usa desde hace tanto que pocas veces se las diferencia. Algo más rápida, tanto por su estructura(el modo de pagina rápida) como por ser de 70 ó 60 nanosegundos.

Usada hasta con los primeros Pentium, físicamente aparece como SIMMs de 30 ó 72 contactos.

- EDO: o EDO - RAM, extended data output - RAM. Evoluciona de la Fast Page; permite empezar a introducir nuevos datos mientras los anteriores estan saliendo, lo que la hace algo mas rapida. Muy común en los Pentium MMX y AMD K6, con refrescos de 70, 60 ó 50nonasegundos. Se instala sobre todo en SIMMs de 72 contactos, aunque existe en forma de DIMMs de 168 contactos.B: Cuáles son las diferencias entre las memorias RAM Y ROM.Dentro de las Memorias físicas en nuestro Hardware, existen dos tipos en función de lectura/escritura o solamente lectura: la Memoria RAM y la Memoria ROM, aunque se diferencien sólo con una letra (a != o), también tienen diferencias técnicas que ampliaré a continuación.La Memoria RAM es la que todos conocemos, pues es la memoria de acceso aleatorio o directo; es decir, el tiempo de acceso a una celda de la memoria no depende de la ubicación física de la misma (se tarda el mismo tiempo en acceder a cualquier celda dentro de la memoria). Son llamadas también memorias temporales o memorias de lectura y escritura.En este tipo particular de Memoria es posible leer y escribir a voluntad. La Memoria RAM está destinada a contener los programas cambiantes del usuario y los datos que se vayan necesitando durante la ejecucón y reutilizable, y su inconveniente radica en la volatilidad al contrtarse el suministro de corriente; si se pierde la alimentación eléctrica, la información presente en la memoria también se pierde.Por este motivo, surge la necesidad de una memoria que permanentemente, guarde los archivos y programas del usuario que son necesarios para mantener el buen funcionamiento del sistema que en se ejecute en la misma.La Memoria ROM nace por esta necesidad, con la característica principal de ser una memoria de sólo lectura, y por lo tanto, permanente que sólo permite la lectura del usuario y no puede ser reescrita.Por esta característica, la Memoria ROM se utiliza para la gestión del proceso de arranque, el chequeo inicial del sistema, carga del sistema operativo y diversas rutinas de control de dispositivos de entrada/salida que suelen ser las tareas encargadas a los programas grabados en la Memoria ROM. Estos programas (utilidades) forman la llamada Bios del Sistema.Entonces, en conclusión:

- - La Memoria RAM puede leer/escribir sobre sí misma por lo que, es la memoria que utilizamos para los programas y aplicaciones que utilizamos día a día

- - La Memoria ROM como caso contrario, sólo puede leer y es la memoria que se usa para el Bios del Sistema.

- C: Qué es el CMOS, ROM-BIOS.

- D: Cuáles son las funciones del BIOS

- La BIOS cumple un papel fundamental en el funcionamiento de nuestro PC, siendo el único dispositivo que conoce realmente el hardware de nuestro ordenador y el que se encarga de su inicialización.

El arranque del PC se realiza a través de la BIOS, cargándose un software de control en cada arranque, el cual se encarga de realizar un testeo del hardware del ordenador a fin de verifiar y por fin argar el SO en la memoria.

Igualmente, existen unos archivos que configurarán el ordenador de acuerdo a ciertas peculiaridades, realizándose a través de los ficheros denominados CONFIG.SYS y AUTOEXEC.BAT.

La existenia de estos archivos no es precisa para el arranque del PC, pudiendo éste arrancar normalmente sin ellos.

Así pues, la BIOS arranca en dos fases:

- Primero realiza un reconocimiento y testeo del hardware presente en el ordenador.

- Posteriormente realiza el arranque del SO, para lo cual debe cargar en memoria ciertas rutinas a fin de comuniarse con los distintos dispositivos hardware.

Códigos de error de la BIOS

Si durante el proceso de testeo del hardware la BIOS detecta alguna anomalía, nos lo hará saber mediante un sistema de pitidos.

Este código no está estandarizado y cada fabricante tiene sus normas.

Actualización de la BIOS

La BIOS es un ciruito integrado que contine un programa. Con el tiempo surgen nuevas funciones y se corrigen defectos por lo cual las firmas comerciales pueden sacar nuevas versiones a fin de actualizar nuestra BIOS.

Principales fabricantes de BIOS

Existen muy pocos fabricantes de BIOS- E: Cuáles son las características de las memorias dinámicas y estáticas

- 1) con sus propias palabras explique el funcionamiento de la memoria dinámica y memoria estática

Memoria dinámica

Es memoria que se reserva en tiempo de ejecución. Su tamaño puede variar durante la ejecución del programa y puede ser liberado mediante la función free.

Memoria estática

Es el espacio de memoria que se crea al declarar variables, arrays o matrices de forma estática (ej. int x, char c[MAX], etc.) y cuyo tamaño no podemos modificar durante la ejecución del programa ni liberar el espacio que ocupa.

La memoria RAM estática es rápida y cara, y la memoria RAM dinámica es más barata pero algo más lenta. Por ello, la RAM estática se usa para crear la caché de alta velocidad en la CPU, mientras que la RAM dinámica forma el extendido espacio del sistema RAM.

2) diferencia entre memoria estática y memoria dinámica

Memoria estática, es cuando, por ejemplo, escribes un programa en cualquier lenguaje, pero dentro de ese lenguaje, en base a su sintaxis, reservas memoria para una variable local, global, char, int, long, sea el tipo que sea y tamaño que sea, pero quieres reservar memoria y tienes que anteponer una palabra reservada del lenguaje en el que lo escribas, así, el sistema te va a reservar ciertos bytes de tu memoria y ningún otro programa podrá "invadir" ese espacio en memoria.

Memoria dinámica, es lo contrario, es decir, que tu cuando declaras una variable como dinámica, el sistema va...- F: Cuál es la función principal de la memoria caché y cuantos tipos de caché hay.

- Los ordenadores tienden a utilizar las mismas instrucciones y (en menor medida), los mismos datos repetidamente.

- La información necesitada se encuentra almacenada de forma adyacente, o cuando menos muy cercana, en memoria o disco.

- Discriminar que información debe ser almacenada y cual descartada.

- Decidir la organización interna de este almacenamiento.

- Manejar las peticiones de lectura. Esto exige disponer de un mecanismo de intercepción de las peticiones del dispositivo que está siendo cacheado.

- Manejar las peticiones de escritura. Interceptar las peticiones de escritura del dispositivo a cachear.

- CAS: indica el tiempo que tarda la memoria en colocarse sobre una columna o celda.

- RAS: indica el tiempo que tarda la memoria en colocarse sobre una fila.

- ACTIVE: indica el tiempo que tarda la memoria en activar un tablero.

- PRECHARGE: indica el tiempo que tarda la memoria en desactivar un tablero.

- Mandar una señal para activar el tablero y esperar a que termine el tiempo de activación (latencia ACTIVE).

- Mandar una señal para saber cuál es la fila en la que se debe posicionar y esperar a su latencia (latencia RAS).

- Mandar una señal para saber cuál es la columna o celda donde se debe posicionar y esperar (latencia CAS).

- 1 X ACTIVE (ya que se leen menos de 64 celdas, que son las que tiene el tablero completo)

- 3 X RAS (ya que cada fila tiene 8 posiciones)

- 20 X CAS (ya que se van a leer 20 celdas)

- 1/133 * 10^6 = 7.5 * 10^-9 = 7.5 ns

- 1/200 * 10^6 = 6 * 10^-9 = 6 ns

- Sistema 133 MHz --> 2 – 2 – 2 – 5 --> CAS, RAS, PRECHARGE y ACTIVE

- Sistema 200 MHz --> 3 – 2 – 2 – 5 --> CAS, RAS, PRECHARGE y ACTIVE

- Sistema 133 MHz

- Sistema 200 MHz

- Sistema 133 MHz

- Sistema 200 MHz

Una memoria caché es una memoria enla que se almacenas una serie de datos para su rápido acceso. Existen muchas memorias sistema, incluso de datos, como es caché (de disco, deel caso de la caché de Google), pero en este tutorial nosvamos a centrar en la caché de los procesadores.Básicamente, la memoria caché de un procesador es un tipo de memoria volátil (del tipo RAM), pero de una gran velocidad. En la actualidad esta memoria está integrada en el procesador, y su cometido es almacenar una serie de instrucciones y datos a los que el procesador accede continuamente, con la finalidad de que estos accesos sean instantáneos. Estas instrucciones y datos son aquellas a las que el procesador necesita estar accediendo de forma continua, por lo que para el rendimientodel procesador es imprescindible que este acceso sea lo más rápido y fluido posible.Con el objetivo de lograr un tiempo de acceso menor a los datos almacenados en distintos tipos de memoria, existen sistemas de hardware o software llamados caché, los cuales almacenan estos datos de forma duplicada. La memoria caché contenida dentro de una CPUmemoria RAM o memoria principal de la computadora, y es por esta razón que mejora la capacidad de procesamiento del mismo.Cada vez que se accede por vez primera a determinado dato, este es almacenado en caché, posteriormente al intentar leer el mismo dato se recurrirá a la información almacenada en caché, ahorrando tiempo de acceso. La memoria caché se renueva, por lo tanto, a todo momento.Los discos duros y otros dispositivos de almacenamiento también hacen utilización de estos métodos, ya sea por hardware y/o por software mediante el sistema operativo, el cual destina cierta parte de su memoria RAM al almacenamiento de información proveniente de estos dispositivos. Las grabadoras de CD/DVD poseen una memoria caché que va almacenando los datos previamente a ser grabados en discos ópticos, e incluso algunos programas brindan un caché extra para evitar aún más la inutilización de los discos.La forma en que un bloque se coloca en memoria caché puede ser directa, asociativa, o asociativa por conjuntos, su extracción es por demanda o con prebúsqueda, su reemplazo puede ser aleatorio o FIFO (el primero que entra es el primero que sale). La actualización de la memoria RAM puede ser inmediata o aplazada.TIPOS

Hay tres tipos diferentes de memoria caché para procesadores:Caché de 1er nivel (L1): Esta caché está integrada en el núcleo del procesador, trabajando a la misma velocidad que este. La cantidad de memoria caché L1 varía de un procesador a otro, estando normalmente entra los 64KB y los 256KB. Esta memoria suele a su vez estar dividida en dos partes dedicadas, una para instrucciones y otra para datos.Caché de 2º nivel (L2): Integrada también en el procesador, aunque no directamente en el núcleo de este, tiene las mismas ventajas que la caché L1, aunque es algo más lenta que esta. La caché L2 suele ser mayor que la caché L1, pudiendo llegar a superar los 2MB. A diferencia de la caché L1, esta no está dividida, y su utilización está más encaminada a programas que al sistema.Caché de 3er nivel (L3): Es un tipo de memoria caché más lenta que la L2, muy poco utilizada en la actualidad. En un principio esta caché estaba incorporada a laplaca base, no al procesador, y su velocidad de acceso era bastante más lenta que una caché de nivel 2 o 1, ya que sibien sigue siendo una memoria de una gran rapidez (muy superior a la RAM, y mucho más en la época en la que se utilizaba), depende de la comunicación entre el procesador y la placa base. Para hacernos una idea más precisa de esto, imaginemos en un extremo el procesador y en el otro la memoria RAM. Pues bien, entre ambos se encuentra la memoria caché, más rápida cuanto más cerca se encuentre del núcleo del procesador (L1).Las memorias caché son extremadamente rápidas (su velocidad es unas5 veces superior a la de una RAM de las más rápidas), con la ventaja añadida de no tener latencia, por lo que su acceso no tiene ninguna demora... pero es un tipo de memoria muy cara. Esto, unido a su integración en el procesador (ya sea directamente en el núcleo o no) limita bastante el tamaño, por un lado por lo que encarece al procesador y por otro por el espacio disponible. En cuanto a la utilización de la caché L2 en procesadores multinucleares, existen dos tipos diferentes de tecnologías a aplicar.Por un lado está la habitualmente utilizada por Intel, que consiste en que el total de la caché L2 está accesible para ambos núcleos y por otro está la utilizada por AMD, en la que cada núcleo tiene su propia caché L2 dedicada solo para ese núcleo. La caché L2 apareció por primera vez en los Intel Pentium Pro, siendo incorporada a continuación por los Intel Pentium II, aunque en ese caso no en el encapsulado del procesador, sino externamente (aunque dentro del procesador)Imagen de un P-II, en la que se puede observar los chips de la caché L2.Desde la aparición en el mercado de procesadores con frecuencia de reloj de 25 o incluso 33 MHz o mas, una memoria de trabajo constituida por RAM dinámica ya no esta preparada para satisfacer las exigencias dela CPU en términos de tiempo de acceso. Con esas frecuencias,el procesador se ve forzadoa aguardar continuamente hasta que la memoria detrabajo reaccione, lo cual conlleva que su capacidad operativa no sea aprovechada al máximo.

En principio, la memoria de trabajo debería poder ser sustituida completamente por componentes estáticos de RAM que permitiesen intervalos de acceso bastante más breves. Pero esto seria demasiado caro. Por eso, en los casos en relación a equipos 386 y 486 de altas frecuencias, se ha recurrido a un método que ya se utilizaba en las gigantescas computadoras de los años setenta: la instalación de una RAM cacheexterna . "Externa" quiere decir, en este contexto, que se sitúa fuera de la CPU, en su entorno y unida aella por el sistema bus. En los 486, la memoria caché, que estamos describiendo recibe también el nombre de "caché, de segundo nivel", se ubica físicamente sobre laplaca madre y consta de una serie de componentes est ticos de RAM con una capacidad de64 o 256 kilobits. Así pues, con este procedimiento pueden obtenerse cachés de 64 o 256 kilobytes, tamaño bastante inferior al de la memoria de trabajo. La vigilancia de la memoria cachécorre a cargodel controlador caché 82385 de Intel.El funcionamiento de la RAM cache

La RAM caché está, pues, situada entre la CPU y la memoria de trabajo y opera a modo de memoria intermedia. Dado que las computadoras compatibles IBM procesan las instrucciones de forma secuencial (por orden de llegada), los mejores programas son los escritos partiendo del "principio de localidad". Este principio determina que al ponerse en marcha el programa se utilicen partes de memoria de un sector inmediato, ubicadas en serie y lo más cerca posible unas de otras.

La RAM caché está, pues, situada entre la CPU y la memoria de trabajo y opera a modo de memoria intermedia. Dado que las computadoras compatibles IBM procesan las instrucciones de forma secuencial (por orden de llegada), los mejores programas son los escritos partiendo del "principio de localidad". Este principio determina que al ponerse en marcha el programa se utilicen partes de memoria de un sector inmediato, ubicadas en serie y lo más cerca posible unas de otras.

Los saltos a zonas de la memoria más alejadas ("far jumps") son poco frecuentes. Para activar un bucle de programación quevaya a ejecutarse con asiduidad, debe extraerse de la memoria una y otra vez la misma instrucción. La memoria caché funciona de forma que ante una solicitud de la CPU, el fragmento de la memoria a leer y el que le sigue han de ser cargados primero en la memoria caché y luego enviados a la CPU. Cualquierusuario que conozca las bases técnicas de la programación sabe que la próxima solicitud de la CPU hará referencia al mismo sector de la memoria o a uno vecino del anteriormente consultado. Así, con este método al memoria caché puede satisfacer, en la mayoría absoluta de los casos, las consultas formuladas. Si no dispusiéramos de ella, la memoria de trabajo tendría, una vez mas, que pasar a la acción.

El procedimiento descrito optimiza, asimismo, los accesos del procesador a la memoria de trabajo. El aprovechamiento de la operatividad de los procesadores de alto rendimiento depende, así, de la capacidad que tenga la memoria caché de satisfacer a la CPU. Frente a unfallo de la caché la CPU se ve obligada a recurrir a la relativamente mas lenta memoria de trabajo. Los fabricantes de placas madre utilizan estrategias de caché muy diversas.

Las diferencias residen en la manera de almacenar y localizar los datos y los usos que se le dan al contenido de esta memoria. También los procesos de reproducción, es decir, los principios que rigen el modo de copiar la memoria de trabajo sobre la caché, pueden diferir unos de otros. Las dimensiones de la memoria caché son igualmente importantes, pero novamos a recrearnos aquí ¡sobre las peculiaridades que distinguen a un principio de reproducción asociativo total de uno parcial. En resumen puede decirse que las placas con una frecuencia idéntica pero con o sin caché, externa son tan diferentes como la noche del día. Solo mediante una RAM caché puede aprovecharse de forma realtoda la capacidad de un procesador. Incluso en las placas 386SX las diferencias mencionadas se hacen palpables.

Respecto a las dimensiones de la memoria caché, cabe señalar que una computadora con el DOS tiene mas que suficiente con 64 Kb (es el tamaño ideal). Comparaciones efectuadas revelaron que, por ejemplo, un 486 que operebajo el DOS se vera alentizado en proporción a las dimensiones de la caché instalada. El rendimiento del mismo, tras la ampliación de una memoria caché de 64 a 256 kilobytes se redujo en un 10% aproximadamente. Bajo el OS/2, en cambio, se constató un claro aumento de la capacidad operativa.Aunque de origen inglés , la palabra cache ha tomado carta de naturaleza en Español (no se si los académicos se habrán enterado de ello, por si acaso, la españolizamos añadiéndole un acento). Utilizada en informática significa memoria temporal; generalmente de existencia oculta y automática para el usuario, que proporciona acceso rápido a los datos de uso más frecuente o previsible. Por ejemplo, el "Caché" de disco es un área de memoria donde el Sistema transfiere los datos que supuestamente serán accedidos de inmediato. Si leemos un "cluster" [1] el sistema puede disponer en esta memoria "cache" los clusters que siguen en la estructura lógica, de forma que, si seguimos efectuando lecturas, lo más probable es que los próximos datos estén ya en memoria y puedan ser accedidos de forma inmediata.La utilización de este tipo de memorias no es sino la generalización de un principio de uso común en la vida diaria; poner más a mano las cosas de uso más frecuente. Se basa en dos suposiciones que generalmente resultan ciertas:§2 Tipos de cacheDesde el punto de

es un área de memoria donde el Sistema transfiere los datos que supuestamente serán accedidos de inmediato. Si leemos un "cluster" [1] el sistema puede disponer en esta memoria "cache" los clusters que siguen en la estructura lógica, de forma que, si seguimos efectuando lecturas, lo más probable es que los próximos datos estén ya en memoria y puedan ser accedidos de forma inmediata.La utilización de este tipo de memorias no es sino la generalización de un principio de uso común en la vida diaria; poner más a mano las cosas de uso más frecuente. Se basa en dos suposiciones que generalmente resultan ciertas:§2 Tipos de cacheDesde el punto devista del hardware, existen dos tipos de memoria cache; interna y externa. La primera, denominada también cache primaria, caché de nivel 1 o simplemente caché L1 (Level one) La segunda se conoce también como cache secundaria, cache de nivel 2 o cache L2Desde el punto de vista funcional, existen cachés específicas de algunos dispositivos, por ejemplo, de disco. También se distingue entre caché de lectura y de escritura.§2.1 Caché internaEs una innovación relativamente reciente [3]; en realidad son dos, cada una con una misión específica: Una para datos y otra para instrucciones. Están incluidas en el procesador junto con su circuitería de control, lo que significa tres cosas: comparativamente es muy cara; extremadamente rápida, y limitada en tamaño (en cada una de las cachés internas, los 386 tenían8 KB; el 486 DX416 KB, y los primeros Pentium 8 KB). Como puede suponerse, su velocidad de acceso es comparable a la de los registros, es decir, centenares de veces más rápida que la RAM.§2.2 Caché externaEs más antigua que la interna, dado que hastafecha "relativamente" reciente estas últimas eran impracticables. Es una memoria de acceso rápido incluida en la placa base, que dispone de su propio bus y controlador independiente que intercepta las llamadas a memoria antes que sean enviadas a la RAM ( H2.2 Buses locales).La caché externa típica es un banco SRAM ("Static Random Access Memory") de entre 128 y 256 KB.Esta memoria es considerablemente más rápida que la DRAM ("Dynamic Random Access Memory") convencional, aunque también mucho más cara [5] (tenga en cuenta que un aumento de tamaño sobre los valores anteriores no incrementa proporcionalmente la eficacia de la memoria caché). Actualmente (2004) la tendencia es incluir esta caché en el procesador. Los tamaños típicos oscilan entre 256 KB y 1 MB.Nota: En 1997, con la introducción del procesador Pentium II, Intel abandonó el denominado zócalo7 utilizado hasta entonces en sus procesadores, en favor del denominado Slot-1. La razón argüida era precisamente la inclusión de la caché L2 en la cápsula del procesador.§3 Caché de discoAdemás de las anteriores, que son de propósito general, existe una caché de funcionalidad específica que se aloja en memoria RAM estándar. Es la caché de disco (nos hemos referido a ella en la introducción de este epígrafe), destinada a contener los datos de disco que probablemente sean necesitados en un futuro próximo y los que deben ser escritos. Si la información requerida está en chaché, se ahorra un acceso a disco, lo que es centenares de veces más rápido (recuerde que los tiempos de acceso a RAM se miden en nanosegundos y los de disco en milisegundosE1.7.1 Unidades de medida).Nota: Existe un mecanismo parecido al de caché de disco que aquí se describe pero que funciona en sentido inverso. Es decir, aloja en disco los datos que no pueden ser almacenados en la memoria RAM. Es el sistema de memoria virtual, al que nos referiremos al tratar de la memoria.El funcionamiento de la caché de disco se basa en dos esquemas de operación. La lectura adelantada("Read-ahead") y la escritura retrasada ("Write-behind"). La primera consiste en anticipar lo que se necesitará de forma inmediata y traerlo a la caché. Por su parte, la escritura retrasada consiste en mantener los datos en caché hasta que se producen momentos de desocupación del sistema de disco. En este caso la caché actúa como memoria tampón o "buffer" intermedio, y no se obliga al subsistema a realizar físicamente ninguna escritura, con lo que las cabezas quedan libres para nuevas lecturas.Puesto que los cachés de disco de escritura retrasada mantienen los datos en memoria volátil después que "supuestamente" se han escrito en el dispositivo, una caída accidental del sistema, por fallo de energía o apagado intempestivo, puede producir pérdidas de los datos alojados en la caché en ese momento (es esta una de las razones por las que los sistemas Windows y Linux exigen un proceso especial de apagado, que a veces tarda unos segundos, en los que observamos una intensa actividad del sistema de disco).Nota: La mayoría de los lenguajes disponen de métodos para forzar una escritura "real" de los datos vaciando la caché de disco; suelen ser sentencias del tipo commit, flush etc. Es una práctica de seguridad aconsejable, y señal de programación cuidadosa, realizar un vaciado de "buffers" después de cada transacción importante siempre que las circunstancias lo permitan§3.1 Caché de disco en MS DOS y WindowsLa cache de los sistemas MS DOS y de los primeros sistemas Windows se denominaba SmartDrive. Por su parte, los nuevos Sistemas de32 bits disponen de un controlador virtual denominado VCACHE que utiliza un esquema de funcionamiento de lectura adelantada y escritura atrasada para proporcionar servicios de cache a las máquinas virtuales (E0.2).VCACHE tiene la ventaja cachear ficheros en discos de red, y de permitir cambiar en tiempo de ejecución la cantidad de memoria destinada a este menester. Cuando la actividad del disco es elevada pero la ocupación de memoria es baja, VCACHE incrementa su tamaño para realizar la mayor cantidad de operación en RAM, evitando de este modo accesos a disco. Por ejemplo, si la aplicación abre un fichero para lectura/escritura, es posible que VCACHE vuelque la totalidad del fichero a memoria; posteriormente, quizás cuando se cierre el fichero, la imagen de memoria sea volcada de nuevo al disco.Si por el contrario la actividad de disco es pequeña y la ocupación de memoria es alta, VCACHE disminuye su propio tamaño con objeto de

para proporcionar servicios de cache a las máquinas virtuales (E0.2).VCACHE tiene la ventaja cachear ficheros en discos de red, y de permitir cambiar en tiempo de ejecución la cantidad de memoria destinada a este menester. Cuando la actividad del disco es elevada pero la ocupación de memoria es baja, VCACHE incrementa su tamaño para realizar la mayor cantidad de operación en RAM, evitando de este modo accesos a disco. Por ejemplo, si la aplicación abre un fichero para lectura/escritura, es posible que VCACHE vuelque la totalidad del fichero a memoria; posteriormente, quizás cuando se cierre el fichero, la imagen de memoria sea volcada de nuevo al disco.Si por el contrario la actividad de disco es pequeña y la ocupación de memoria es alta, VCACHE disminuye su propio tamaño con objeto deaumentar la RAM disponible para las aplicaciones.§3.2 Vaciado de buffers en C++En la terminología C++ los flujos que son cacheados se denominan "buffered". A este respecto, los compiladores C/C++ disponen de su propio sistema de caché para ficheros de disco. Esta caché se denominade ejecución (runtime), para distinguirla de la caché del Sistema. Así mismo, disponen de recursos en la Librería Estándar para forzar su vaciado en caso necesario; para esto se recurre a la funciones fflush (para ficheros abiertos con fopen) y flush (para los flujos de salida, "ostreams").Sin embargo, no olvide que el vaciado de la caché del compilador se realiza sobre la del Sistema, que está por debajo (recuerde que el Software tiene una estructura de capas E1.7w1), y que el SO decide por su cuenta cuando es el momento oportuno para realizar físicamente la escritura de los discos. Esto significa que una seguridad total solo se alcanza forzando la escritura de la caché del Sistema, y esto naturalmente depende de la plataforma utilizada.Nota: Además de las posibilidades ofrecidas en la Librería Estándar, el compilador MS Visual C++ para Windows ofrece la función _flushall, que fuerza el vaciado de la caché de ejecución de todos los ficheros abiertos. También dispone de la librería COMMODE.OBJ, que enlazada con la aplicación, fuerza que las llamadas a fflush y a _flushall escriban directamente los buffers al disco en vez de a la caché del Sistema.El siguiente ejemplo

E1.7w1), y que el SO decide por su cuenta cuando es el momento oportuno para realizar físicamente la escritura de los discos. Esto significa que una seguridad total solo se alcanza forzando la escritura de la caché del Sistema, y esto naturalmente depende de la plataforma utilizada.Nota: Además de las posibilidades ofrecidas en la Librería Estándar, el compilador MS Visual C++ para Windows ofrece la función _flushall, que fuerza el vaciado de la caché de ejecución de todos los ficheros abiertos. También dispone de la librería COMMODE.OBJ, que enlazada con la aplicación, fuerza que las llamadas a fflush y a _flushall escriban directamente los buffers al disco en vez de a la caché del Sistema.El siguiente ejemplomuestra algunas formas de vaciado de los buffers del compilador y de la caché del SistemaL.5 abre el fichero Fichero1 para lectura y escritura.Lallamada a fflush en L.6 fuerza al programa a vaciar al SO la caché de ejecución asociados al fichero1.La llamada a _commit en L.7 obliga al cache de disco del Sistema vaciar sus buffers.L.11 se instancia un objeto Fichero2 de la plantilla basic_ofstream, para realizar escritura.La línea L.12 invoca el método flush para dicho objeto. Esta invocación fuerza al programa a vaciar al SO los buffers de ejecución asociados con Fichero2.La invocación a _commit en L.13 obliga al caché de disco del Sistema a vaciar los buffers al disco. Esta función requiere un manejador "handle" referido al fichero; en este caso, el manejador se obtiene mediante una invocación al método rdbuf. ofstream.rdbuf()->fd().Nota: _commit es una función de MS Visual C++ que obliga al Sistema a vaciar los buffers de un fichero determinado. No es estándar C++ y solo funciona en Sistemas MS de 16 bits. En los de 32 bits se recurre a la librería Commode.obj según se ha indicado§4 Rendimiento de la cachéEl funcionamiento de la caché de lectura se parece al de un adivino; debe anticipar lo que ocurrirá en el futuro. Si el dispositivo que está siendo cacheado encuentra los datos en la caché, habrá un éxito ("hit"), en caso contrario, un fracaso ("miss"). Los sistemas de caché actuales son capaces de proporcionar una tasa de éxitos superior al 90%.Como puede figurarse el lector,construir un mecanismo de caché no es una tarea baladí. Se requieren esquemas de funcionamiento que atiendan de forma simultanea y balanceada diversos factores:§5 Caché oportunistaExiste un tipo especial que podríamos considerar "de aplicación", denominada caché oportunista("Opportunistic cache"). Está relacionada con los problemas de bloqueos de ficheros en entornos multiusuario en los que distintas aplicaciones pueden acceder a los mismos datos.En estos casos, los Sistemas Operativos disponen de mecanismos para que un usuario (programa de aplicación) obtenga el bloqueo de todo un fichero o parte de él. La teoría es que mientras se mantenga el bloqueo, ningún otro usuario puede modificar el fichero (tal vez si leerlo), y que una vez finalizadas las modificaciones, el usuario desbloquea el fichero para que otros puedan utilizarlo. Sin embargo, en determinadas aplicaciones de red, y con objeto de aumentar el rendimiento, se utiliza un sistema mixto denominado bloqueo oportunista oplock ("Opportunistic locking"), en el que el usuario comunica al Sistema que utilizará esta modalidad[6]. Para ello, obtiene unacopia de la totalidad del fichero, que almacena un una cachélocal oportunista. De esta forma, las operaciones son más rápidas que si tiene que realizarse a través de la red las peticiones de distintos trozos, junto con las correspondientes solicitudes de bloqueo/desbloqueo. Finalmente, cuando el usuario ha finalizado las operaciones con el fichero, devuelve al servidor una copia actualizada.El problema se presenta cuando, en el intermedio, otro usuario solicita utilizar el mismo fichero. La incidencia es especialmente frecuente cuando el fichero a manejar es muy grande. Porque entonces, incluso para una pequeña modificación, el primer usuario puede demorarse bastante en devolver la versión modificada al servidor. La solución adoptada para evitar demoras excesivas, consiste en que, al recibir la petición del segundo usuario, el Sistema envía al primero una orden de interrumpir el oplock y devolver el fichero tal como está en ese momento para que el segundo usuario pueda utilizarlo.Aunque no exento de problemas, especialmente en redes poco fiables, el sistema permite aumentos del rendimiento del orden del 30%. No tanto por el sistema de bloqueo utilizado, como por el hecho de que los datos hayan sido previamente cacheados por el usuario.[1] También denominado "Allocation Unit" o unidad de asignación en Español. Es el conjunto de sectores de disco que son tratados por el sistema como una sola unidad de almacenamiento. Su tamaño (número de sectores de disco) depende del SO y del tamaño de la partición lógica (MS DOS y Windows utilizan un cluster de 1 sector en los disquetes de 3.5"). Un "Cluster" puede estar ocupado o disponible, pero no parcialmente ocupado.El Sistema de Archivo de un Sistema Operativo es precisamente una forma decontrolar , asignar, desasignar y acceder clusters para alojar ficheros en disco."Cluster" tiene también otra acepción en inglés: Designar un almacenamiento redundante de datos en sistemas distintos.Hasta hace pocos años, en que la tecnología de discos ha producido unidades extremadamente silenciosas, a un oído experimentado le bastaba escuchar la "música" de los servos para saber si el sistema de "cache" de disco estaba instalado o no.[3] Introducida con el Intel 386 SLC que tenía una cache interna para instrucciones y datos, mientras que en los Pentinum® instrucciones y datos disponen de cachés separadas.[4] Bueno, eso es lo que yo creía porque aprendí la palabreja de textos ingleses, pero D. Julián Cirielli, desde Bs. As. Argentina, me aclara amablemente que en realidad, la palabra proviene del francés, y significa escondite/escondida. He preferido mantener intacta mi errónea redacción anterior e incluir aquí la corrección junto con mi agradecimiento.[5] El motivo es la propia construcción de la memoria estática, constituida por conjuntos de seis transistores por cadabit almacenado, lo que las hace mucho más voluminosas (y caras) que las memorias dinámicas de capacidad comparable; estas últimas están consituidas por un conjunto de 1 transistor y un condensador por cada bit. Ladescarga del condensador es lo que hace que requieran una actualización (refresco) cada15 &µs (microsegundos) aproximadamente, lo que añade una dificultad adicional, pues durante la actualización el sistema queda paralizado (en el bus hay una línea específica, DACK-0, para indicar que se está produciendo este refresco de la memoria dinámica H2).Actualmente (2001), las SRAM tienen tiempos de acceso del orden de 2 a 15 ns (nanosegundos), mientras que en las DRAM es del orden de 60 ns.[6] Por ejemplo, Samba el popular sistema Linux para compartir recursos sobre redes TCP/IP, puede utilizar este tipo de caché oportunista con sus clientes.H: Cuáles son los tipos, velocidades y capacidades que manejan las memorias DIMM.Significado de memoria DIMM - SDRAM DIMM proviene de ("Dual In line Memory Module"), lo que traducido significa módulo de memoria de línea dual (este nombre es debido a que sus contactos de cada lado son independientes, por lo tanto el contacto es doble en la tarjeta de memoria): son un tipo de memorias DRAM (RAM de celdas construidas a base de capacitores), las cuáles pueden tener chips de memoria en ambos lados de la tarjeta ó solo de un lado, cuentan con un conector especial de 168 terminales para ranuras de la tarjeta principal (Motherboard). Cabe destacar que la característica de las memorias de línea dual, es precursora de los estándares modernos RIMM y DDR-X), por ello no es de extrañarse que también se les denomine DIMM - SDRAM tipo RIMM ó DIMM - SDRAM DDR-X.aracterísticas generales de la memoria DIMM - SDRAM + Cuenta con conectores físicamente independientes en ambas caras de la tarjeta de memoria, de allí que se les denomina duales. + Todos las memorias DIMM - SDRAM cuentan con 168 terminales. + Cuentan con un par de muescas en un lugar estratégico del conector, para que al insertarlas, no haya riesgo de colocarlas de manera incorrecta. + La memoria DIMM - SDRAM permite el manejo de 32 y 64 bits. + La medida del DIMM - SDRAM es de 13.76 cm. de largo X 2.54 cm. de alto. + Puede convivir con SIMM en la misma tarjeta principal ("Motherboard") si esta cuenta con ambas ranuras.artes que componen la memoria DIMM - SDRAM Los componentes son visibles, ya que no cuenta con cubierta protectora; son básicamente los siguientes:Cuáles son los tipos, velocidades y capacidades que manejan las memorias DDR.Partes que componen la memoria DDR Los componentes son visibles, ya que no cuenta con cubierta protectora; son básicamente los siguientes: Figura 3. Esquema de partes de la memoria RAM tipo DDR1.- Tarjeta: es una placa plástica sobre la cuál están soldadas los componentes de la memoria.2.-Chips: son módulos de memoria volátil.3.- Conector (184 terminales): base de la memoria que se inserta en la ranura especial para memoria DDR.4.- Muesca: indica la posición correcta dentro de la ranura de memoria DDR.Partes de la memoria DDR

Figura 3. Esquema de partes de la memoria RAM tipo DDR1.- Tarjeta: es una placa plástica sobre la cuál están soldadas los componentes de la memoria.2.-Chips: son módulos de memoria volátil.3.- Conector (184 terminales): base de la memoria que se inserta en la ranura especial para memoria DDR.4.- Muesca: indica la posición correcta dentro de la ranura de memoria DDR.Partes de la memoria DDR Conectores - terminales para la ranuraSolo hay una versión física:

Conectores - terminales para la ranuraSolo hay una versión física:Conector Figuras DDR 184 terminales Conector de la memoria

Ranura de la tarjeta principal

Velocidad de la memoria DDRLa unidad para medir la velocidad de las memorias RAM es en MegaHertz (MHz). En el caso de los DDR, tiene varias velocidades de trabajo disponibles, la cuál se tiene que adaptar a la velocidad de trabajo del resto del sistema. Básicamente se comercializaron las siguientes:

Velocidad de la memoria DDRLa unidad para medir la velocidad de las memorias RAM es en MegaHertz (MHz). En el caso de los DDR, tiene varias velocidades de trabajo disponibles, la cuál se tiene que adaptar a la velocidad de trabajo del resto del sistema. Básicamente se comercializaron las siguientes:Nombre asignado Velocidad de la memoria (FSB: "Frontal Side Bus") PC-2100 266 MHz PC-2700 333 MHz PC-3200 400 MHz  Tecnología DDR ECCLa tecnología ECC en memorias DDR se utiliza básicamente para servidores que manejan datos sumamente críticos, ya que no es común su uso en equipos domésticos porque esta tecnología aumenta en gran medida los costos de la memoria.ECC son las siglas de ("Error Code Correction"), que traducido significa código para corrección de errores. Se trata de un código que tiene la capacidad de detectar y corregir errores de 1 ó mas bits, de tal suerte que el usuario no detecta la falla, pero en caso de ser mas de un bit se muestra error de paridad.Esto se logra mediante el uso de un algoritmo matemático de parte del ECC, el cuál se almacena junto con los otros datos, así al ser solicitados estos, se comparará el código almacenado con el que genera la solicitud. En caso de la no coincidencia exacta de lo anterior el código original se decodificará para determinar la falla y se procede a corregirlo.

Tecnología DDR ECCLa tecnología ECC en memorias DDR se utiliza básicamente para servidores que manejan datos sumamente críticos, ya que no es común su uso en equipos domésticos porque esta tecnología aumenta en gran medida los costos de la memoria.ECC son las siglas de ("Error Code Correction"), que traducido significa código para corrección de errores. Se trata de un código que tiene la capacidad de detectar y corregir errores de 1 ó mas bits, de tal suerte que el usuario no detecta la falla, pero en caso de ser mas de un bit se muestra error de paridad.Esto se logra mediante el uso de un algoritmo matemático de parte del ECC, el cuál se almacena junto con los otros datos, así al ser solicitados estos, se comparará el código almacenado con el que genera la solicitud. En caso de la no coincidencia exacta de lo anterior el código original se decodificará para determinar la falla y se procede a corregirlo. Figura 3. Esquema de la memoria RAM tipo DIMM - SDRAM.I: Cuáles son los tipos, velocidades y capacidades que manejan las memorias DDR.

Figura 3. Esquema de la memoria RAM tipo DIMM - SDRAM.I: Cuáles son los tipos, velocidades y capacidades que manejan las memorias DDR.Partes que componen la memoria DDR Los componentes son visibles, ya que no cuenta con cubierta protectora; son básicamente los siguientes: Figura 3. Esquema de partes de la memoria RAM tipo DDR1.- Tarjeta: es una placa plástica sobre la cuál están soldadas los componentes de la memoria.2.-Chips: son módulos de memoria volátil.3.- Conector (184 terminales): base de la memoria que se inserta en la ranura especial para memoria DDR.4.- Muesca: indica la posición correcta dentro de la ranura de memoria DDR.Partes de la memoria DDR

Figura 3. Esquema de partes de la memoria RAM tipo DDR1.- Tarjeta: es una placa plástica sobre la cuál están soldadas los componentes de la memoria.2.-Chips: son módulos de memoria volátil.3.- Conector (184 terminales): base de la memoria que se inserta en la ranura especial para memoria DDR.4.- Muesca: indica la posición correcta dentro de la ranura de memoria DDR.Partes de la memoria DDR Conectores - terminales para la ranuraSolo hay una versión física:

Conectores - terminales para la ranuraSolo hay una versión física:Conector Figuras DDR 184 terminales Conector de la memoria

Ranura de la tarjeta principal

Velocidad de la memoria DDRLa unidad para medir la velocidad de las memorias RAM es en MegaHertz (MHz). En el caso de los DDR, tiene varias velocidades de trabajo disponibles, la cuál se tiene que adaptar a la velocidad de trabajo del resto del sistema. Básicamente se comercializaron las siguientes:

Velocidad de la memoria DDRLa unidad para medir la velocidad de las memorias RAM es en MegaHertz (MHz). En el caso de los DDR, tiene varias velocidades de trabajo disponibles, la cuál se tiene que adaptar a la velocidad de trabajo del resto del sistema. Básicamente se comercializaron las siguientes:Nombre asignado Velocidad de la memoria (FSB: "Frontal Side Bus") PC-2100 266 MHz PC-2700 333 MHz PC-3200 400 MHz  Tecnología DDR ECCLa tecnología ECC en memorias DDR se utiliza básicamente para servidores que manejan datos sumamente críticos, ya que no es común su uso en equipos domésticos porque esta tecnología aumenta en gran medida los costos de la memoria.ECC son las siglas de ("Error Code Correction"), que traducido significa código para corrección de errores. Se trata de un código que tiene la capacidad de detectar y corregir errores de 1 ó mas bits, de tal suerte que el usuario no detecta la falla, pero en caso de ser mas de un bit se muestra error de paridad.Esto se logra mediante el uso de un algoritmo matemático de parte del ECC, el cuál se almacena junto con los otros datos, así al ser solicitados estos, se comparará el código almacenado con el que genera la solicitud. En caso de la no coincidencia exacta de lo anterior el código original se decodificará para determinar la falla y se procede a corregirlo.J: En qué consiste la latencia y cómo interviene en el rendimiento de un computador.

Tecnología DDR ECCLa tecnología ECC en memorias DDR se utiliza básicamente para servidores que manejan datos sumamente críticos, ya que no es común su uso en equipos domésticos porque esta tecnología aumenta en gran medida los costos de la memoria.ECC son las siglas de ("Error Code Correction"), que traducido significa código para corrección de errores. Se trata de un código que tiene la capacidad de detectar y corregir errores de 1 ó mas bits, de tal suerte que el usuario no detecta la falla, pero en caso de ser mas de un bit se muestra error de paridad.Esto se logra mediante el uso de un algoritmo matemático de parte del ECC, el cuál se almacena junto con los otros datos, así al ser solicitados estos, se comparará el código almacenado con el que genera la solicitud. En caso de la no coincidencia exacta de lo anterior el código original se decodificará para determinar la falla y se procede a corregirlo.J: En qué consiste la latencia y cómo interviene en el rendimiento de un computador.Latencia de memorias[editar]

Se denominan latencias de una memoria RAM a los diferentes retardos producidos en el acceso a los distintos componentes de esta última. Estos retardos influyen en el tiempo de acceso de la memoria por parte de la CPU, el cual se mide en nanosegundos (10-9 s) .Resulta de particular interés en el mundo del overclocking el poder ajustar estos valores de manera de obtener el menor tiempo de acceso posible.Estructura física de la memoria[editar]

La memoria está compuesta por un determinado número de celdas, capaces de almacenar un dato o una instrucción y colocadas en forma de tablero de ajedrez. En lugar de tener 64 posibles posiciones donde colocar piezas, tienen n posiciones. No solo existe un "tablero" sino que existen varios, de esta forma la estructura queda en forma de tablero de ajedrez tridimensional.Accesos a memoria[editar]

Cuando se desea acceder a la memoria, es imprescindible indicar el número de tablero, el número de fila dentro del tablero, y el número de columna o celda dentro de esa fila, en ese orden.El tiempo que tarda la memoria en colocarse en la posición necesaria es relativamente pequeño, sin embargo son tantos los datos e instrucciones que se almacenan en la memoria, que al final el proceso puede llegar a hacerse lento.Debido al que se van a leer/escribir muchas cosas de/en la memoria, se necesita un sistema que lea muchas celdas al mismo tiempo, sin transportar los datos de dichas celdas y a continuación, transportar todos los datos a la vez (dato o instrucción ya que es lo único que se almacena en la memoria). Este sistema de leer muchas celdas y después transportar es conocido como bus a ráfagas o burst.Si por cada celda que se leyese, el dato/instrucción se transportara a su destino, la lectura/escritura de memoria sería un proceso demasiado lento.Tipos de latencias[editar]

Existen varios tipos de latencias en las memorias, sin embargo, las más importantes son:Lectura o escritura en memoria[editar]

El proceso a seguir cuando se desea leer o escribir en la memoria será el siguiente:Tiempo de espera[editar]

El tiempo que tarda la memoria en proporcionar el dato, es la suma de las tres latencias: ACTIVE, RAS y CAS.Como se comenta anteriormente, antes de enviar el dato/instrucción a donde deba ir, se deben leer varias celdas de memoria, por lo tanto hay que pasar de una celda a otra, e ir esperando su correspondiente latencia CAS.Si cada tablero tiene, por ejemplo 64 celdas, y se van a leer 20 posiciones, las latencias totales a esperar son:La latencia más importante, como queda patente, es la latencia CAS, y cuanto menor sea esta, mejor rendimiento tendrá el ordenador en general.Tiempo real[editar]

Sea una placa base con Front Side Bus o FSB a 200 MHz. El tiempo de cada ciclo de reloj es: F = 1 / T --> 200 * 10^6 = 1 / T --> T = 1 / 200 * 10^6 --> T = 5 * 10^-9 s = 5 NanoSegundosNOTA: las antiguas memorias RAM que empleaban los Pentium I eran de 70 ns, las EDO que eran las mismas un poco evolucionadas eran de 60 ns, así se puede calcular bastante fácilmente el fsb de aquellos sistemas. Las primeras SDRAM que aparecieron, las PC 100, eran de 10 ns, evidentemente el fsb de aquellos sistemas era de 100 MHz.En función de la calidad de las memorias, sus latencias serán mejores o peores.En la imagen se ve que la memoria tarda 12.5 ns en hacer el CAS, si se cogen 3 ciclos (latencia CAS 3) sobran 2.5 ns. 2.5 en 15 es mucho el 16.6%, y más aun teniendo en cuenta que se hacen muchísimos accesos a memoria, por lo tanto, cuanto más tiempo se ahorre mejor.Al hacer uso de la memoria DDR, se puede emplear tanto el flanco de subida como el de bajada para terminar la latencia, de modo que empleando CAS 2.5 este ejemplo sería óptimo.Latencias vs FSB (caso práctico)[editar]

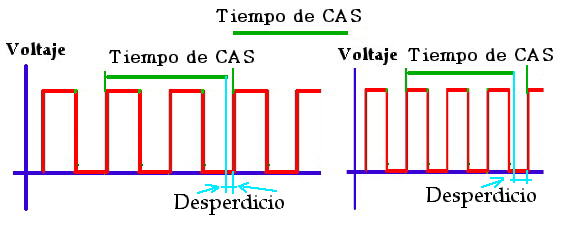

La diferencia de latencia es algo muy apreciable(en especial la latencia CAS) a la hora de medir el rendimiento del ordenador, ya que cuando se accede a memoria tanto para leer como para escribir se tiene que esperar por ella. Por cada celda del tablero que se lea, hay que esperar la latencia CAS, por cada fila completa al RAS, y por cada tablero diferente las ACTIVE y PRECHARGE (a veces se solapan). Se lee/escribe por ráfagas, pero en cada ráfaga se espera ‘x’ veces a CAS, ‘y’ veces RAS, siendo X = Y^2, ACTIVE, PRECHARGE, etc.Por otra parte cuanto más alto sea el FSB, más rendimiento se obtiene. Aunque es una verdad a medias. Las latencias son inversamente proporcionales a la velocidad del bus FSB/HTT, es decir, cuanto mayor FSB maneje el sistema, peor latencia manejará y viceversa. En el dibujo se pueden observar dos sistemas: uno con un FSB de 100 MHz (izquierda) y otro, con un FSB de 200 MHz (derecha), al tener el doble de frecuencia tenemos que en el mismo tiempo se hacen el doble de ciclos, de ahí que a la derecha estén las “ondas” mucho más comprimidas. En ambos casos se emplea la misma memoria, que tarda una tiempo en hacer el acceso CAS. Este tiempo está marcado con una línea verde. La escala de tiempo en ambos casos es exactamente la misma, así que la línea verde será en ambos casos exactamente igual.Para el sistema de la izquierda, se puede ver que el CAS de la memoria es de casi 2 ciclos, para redondear, hay que redondear hacia arriba para darle tiempo a que termine, sobrará un poco, sin embargo, para el caso de la derecha, el CAS sería de 3.

En el dibujo se pueden observar dos sistemas: uno con un FSB de 100 MHz (izquierda) y otro, con un FSB de 200 MHz (derecha), al tener el doble de frecuencia tenemos que en el mismo tiempo se hacen el doble de ciclos, de ahí que a la derecha estén las “ondas” mucho más comprimidas. En ambos casos se emplea la misma memoria, que tarda una tiempo en hacer el acceso CAS. Este tiempo está marcado con una línea verde. La escala de tiempo en ambos casos es exactamente la misma, así que la línea verde será en ambos casos exactamente igual.Para el sistema de la izquierda, se puede ver que el CAS de la memoria es de casi 2 ciclos, para redondear, hay que redondear hacia arriba para darle tiempo a que termine, sobrará un poco, sin embargo, para el caso de la derecha, el CAS sería de 3. En el último dibujo se ve que en la parte de la izquierda se pierde un poco de tiempo desde que se termina el CAS hasta que termina su latencia. Se ve el tiempo desperdiciado abajo a la derecha en color azul claro. Lo mismo pasa en el sistema del dibujo de la derecha. Pero en este caso es más tiempo (La escala temporal, eje de las abscisas, es el mismo en ambos casos, por lo tanto el tiempo es mayor a la derecha).En principio se podría pensar que aunque se pierda un poco más en un lado que en el otro, como el fsb es bastante superior en un lado que en el otro, seguro que es más rápido aun perdiendo un poco de tiempo en el CAS... A continuación se demuestra que esto no es cierto en todos los casos:Un sistema a 133 MHz y otro a 200 MHz, y empleando la misma, exactamente la misma memoria en ambos casos. El tiempo que tarda en ejecutarse un ciclo:Un ciclo en el sistema con bus a 200 MHz tarda 6 nanosegundos en ejecutarse y 7.5 nanosegundos en el sistema con bus a 133 MHz.Suponiendo que la memoria funciona en ambos sistemas con las siguientes latencias:Los tiempos que se tardaría en cada caso serían los siguientes:(2 * 7.5) + (2 * 7.5) + (2 * 7.5) + (5 * 7.5) = 15 + 15 + 15 + 37.5 = 82.5 ns(3 * 6) + (2 * 6) + (2 * 6) + (5 * 6) = 18 + 12 + 12 + 30 = 72 nsHasta aquí parecería que salen mal las cuentas ya que el sistema con bus a 200 MHz tarda menos tiempo, 72 ns frente a 82.5 nsSin embargo, suponiendo que el tablero de la memoria es de 100 filas por 100 columnas las cosas cambian.Recordemos que la latencia CAS se ejecuta tantas veces como columnas haya, en este caso, 100 veces por cada vez que se ejecuta cambio de fila (RAS), por lo tanto, el cálculo justo, suponiendo que hay que leer en una ráfaga justo una fila entera quedaría de la siguiente manera:[100 * (2 * 7.5)] + (2 * 7.5) + (2 * 7.5) + (5 * 7.5) =(15 * 100) + 15 + 15 + 37.5 = 1500 ns + 67.5 ns = 1567.5 ns[100 * (3 * 6)] + (2 * 6) + (2 * 6) + (5 * 6) =(18 * 100) + 12 + 12 + 30 = 1800 ns + 54 ns = 1854 nsEste sería un caso extremo, que justo haya que leer una fila entera y no hubiera que hacer ni un solo salto de fila (RAS) ni cambios de tablero. Aunque aun así podría seguir siendo óptimo el caso del sistema con bus a 133.Con ese cálculo queda clara la importancia de la latencia CAS con respecto a las demás, y la importancia de las latencias con respecto al bus FSB/HTT.1.- Tarjeta: es una placa plástica sobre la cuál están soldadas los componentes de la memoria.2.-Chips: son módulos de memoria volátil.3.- Conector (168 terminales): base de la memoria que se inserta en la ranura especial para memoria DIMM - SDRAM en la tarjeta principal(Motherboard).4.- Muesca: indica la posición correcta dentro de la ranura de memoria.

En el último dibujo se ve que en la parte de la izquierda se pierde un poco de tiempo desde que se termina el CAS hasta que termina su latencia. Se ve el tiempo desperdiciado abajo a la derecha en color azul claro. Lo mismo pasa en el sistema del dibujo de la derecha. Pero en este caso es más tiempo (La escala temporal, eje de las abscisas, es el mismo en ambos casos, por lo tanto el tiempo es mayor a la derecha).En principio se podría pensar que aunque se pierda un poco más en un lado que en el otro, como el fsb es bastante superior en un lado que en el otro, seguro que es más rápido aun perdiendo un poco de tiempo en el CAS... A continuación se demuestra que esto no es cierto en todos los casos:Un sistema a 133 MHz y otro a 200 MHz, y empleando la misma, exactamente la misma memoria en ambos casos. El tiempo que tarda en ejecutarse un ciclo:Un ciclo en el sistema con bus a 200 MHz tarda 6 nanosegundos en ejecutarse y 7.5 nanosegundos en el sistema con bus a 133 MHz.Suponiendo que la memoria funciona en ambos sistemas con las siguientes latencias:Los tiempos que se tardaría en cada caso serían los siguientes:(2 * 7.5) + (2 * 7.5) + (2 * 7.5) + (5 * 7.5) = 15 + 15 + 15 + 37.5 = 82.5 ns(3 * 6) + (2 * 6) + (2 * 6) + (5 * 6) = 18 + 12 + 12 + 30 = 72 nsHasta aquí parecería que salen mal las cuentas ya que el sistema con bus a 200 MHz tarda menos tiempo, 72 ns frente a 82.5 nsSin embargo, suponiendo que el tablero de la memoria es de 100 filas por 100 columnas las cosas cambian.Recordemos que la latencia CAS se ejecuta tantas veces como columnas haya, en este caso, 100 veces por cada vez que se ejecuta cambio de fila (RAS), por lo tanto, el cálculo justo, suponiendo que hay que leer en una ráfaga justo una fila entera quedaría de la siguiente manera:[100 * (2 * 7.5)] + (2 * 7.5) + (2 * 7.5) + (5 * 7.5) =(15 * 100) + 15 + 15 + 37.5 = 1500 ns + 67.5 ns = 1567.5 ns[100 * (3 * 6)] + (2 * 6) + (2 * 6) + (5 * 6) =(18 * 100) + 12 + 12 + 30 = 1800 ns + 54 ns = 1854 nsEste sería un caso extremo, que justo haya que leer una fila entera y no hubiera que hacer ni un solo salto de fila (RAS) ni cambios de tablero. Aunque aun así podría seguir siendo óptimo el caso del sistema con bus a 133.Con ese cálculo queda clara la importancia de la latencia CAS con respecto a las demás, y la importancia de las latencias con respecto al bus FSB/HTT.1.- Tarjeta: es una placa plástica sobre la cuál están soldadas los componentes de la memoria.2.-Chips: son módulos de memoria volátil.3.- Conector (168 terminales): base de la memoria que se inserta en la ranura especial para memoria DIMM - SDRAM en la tarjeta principal(Motherboard).4.- Muesca: indica la posición correcta dentro de la ranura de memoria. - Los ordenadores tienden a utilizar las mismas instrucciones y (en menor medida), los mismos datos repetidamente.

No hay comentarios:

Publicar un comentario